# Proceedings of the 9<sup>th</sup> International SpaceWire and SpaceFibre Conference 2022

AESS

UNIVERSITA

STAR-Dundee 🕸 IEEE

Agenzic

Spaziale Italiana COSA INCENIAIS

# SpaceWire and SpaceFibre 2022

# Proceedings of the 9<sup>th</sup> International SpaceWire and SpaceFibre Conference

# Pisa, Italy, 2022

Editors: Carole Carrie, Pietro Nannipieri and Steve Parkes

SpaceWire and SpaceFibre 2022

Proceedings of International SpaceWire and SpaceFibre Conference

Pisa, Italy, 2022

ISBN: 978-0-9954530-2-9

### © European Space Agency

2022

All rights reserved. No part of this publication may be reproduced or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

#### Preface

These proceedings contain the papers presented at the 9<sup>th</sup> International SpaceWire and SpaceFibre Conference, held in Pisa, Italy between 17<sup>th</sup> and 19<sup>th</sup> October 2022. This Conference brings together international spacecraft engineers and academics who are working on spacecraft on-board data-handling technology. It is of benefit to product designers, hardware engineers, software engineers, system developers and mission specialists, enabling them to share the latest ideas and developments related to SpaceWire and SpaceFibre spacecraft on-board network technologies.

SpaceWire is now being used or designed into well over one hundred spacecraft, covering science, exploration, Earth observation and commercial applications. High profile missions like James Webb Space Telescope, GAIA, ExoMars, BepiColombo, Sentinels 1, 2, 3 and 5 precursor, and GOES-R are using SpaceWire extensively. SpaceWire is being used in Europe, Japan, USA, Russia, China, India, and other countries of the World.

SpaceFibre is the next generation of SpaceWire technology, offering higher data-rates and substantially enhancing the capabilities of SpaceWire. It runs over electrical or fibre optic cable covering distances of 5m and 100 m respectively while running at lane speeds of up to 6.25 Gbit/s currently in radiation tolerant technology. The multi-lane link capability of SpaceFibre results in link speeds of 25 Gbit/s for a quad-lane link with up to 16 lanes per link being possible. Higher lane speeds are also possible. SpaceFibre is not only very fast, it incorporates quality of service, providing multiple independent virtual networks for transferring information over the physical network, each virtual network having its own priority, bandwidth allocation and schedule. These capabilities enable SpaceFibre to provide deterministic data delivery without loss of network bandwidth for combined control and payload data-handling networks. It also provides integrated, rapid fault detection, isolation and recovery technology, which makes SpaceFibre a highly robust network for use in applications where reliability and availability are critical.

The conference covers many different aspects of SpaceWire and SpaceFibre, and includes both academic and industrial presentations. Sessions cover standardisation, components, on-board equipment, test and verification, networks and protocols, and missions and applications. SpaceWire continues to be used extensively and SpaceFibre is gaining momentum, already being designed into spaceflight systems with the first missions in orbit. It is an exciting time in the SpaceWire community as this latest technology literally begins to take off.

The conference committee would like to acknowledge the support and hard work of the many individuals who made 9<sup>th</sup> International SpaceWire and SpaceFibre Conference possible. Originally planned for 2020 we are grateful that the global flood of pandemic has subsided sufficiently for the conference to go ahead in person in 2022. We appreciate the high-quality and inspiring contributions from the authors and the keynote speakers. We express our gratitude to the Technical Committee for their assistance in the review process. We recognise the support from the University of Pisa, IngeniArs, the European Space Agency and STAR-Dundee. Finally, we would like to give a special thanks to the conference organiser Carole Carrie (STAR-Dundee Ltd.), and the local organisers Pietro Nannipieri (University of Pisa) and Camilla Giunti (IngeniArs).

The Conference Chairpersons,

Luca Fanucci (University of Pisa), Steve Parkes (STAR-Dundee Ltd.), Felix Siegle (European Space Agency).

### 2022 Technical Committee

Barthelemy Attanasio - Thales Alenia Space, France

Thomas Bahls - DLR, Germany

Markus Bihler - DLR, Germany

Clifford Kimmery - USA

Daniele Davalle, Ingeniars Srl., Italy

Walter Errico: Sitael, Italy

Luca Fanucci, University of Pisa, Italy

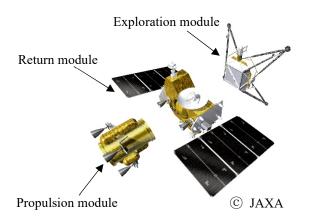

Seisuke Fukuda – JAXA/ISAS, Japan

Hiroki Hihara – NEC, Japan

Jørgen Ilstad - ESA, The Netherlands

David Jameux - ESA, The Netherlands

Alexander Kisin - NASA GSFC, USA

Robert Klar - South West Research Institute, USA

Paolo Lombardi – Leonardo, Italy

Jim Lux - NASA JPL, USA

Giorgio Magistrati - ESA, The Netherlands

Keiichi Matsuzaki - JAXA, Japan

Silvia Moranti - ESA, The Netherlands

Pietro Nannipieri, University of Pisa, Italy

Masaharu Nomachi – University of Osaka, Japan

Steve Parkes - STAR-Dundee Ltd, UK

Paul Rastetter - Airbus GmbH, Germany

Krzysztof Romanowski - ITTI, Poland

Toru Sasaki – Mitsubishi Electric, Japan

Derek Schierlmann - Naval Research Laboratory, USA

Luca Serafini – Kayser Italia Srl., Italy

Felix Siegle - ESA, The Netherlands

Antonis Tavoularis - ESA, The Netherlands

Michael Walshe - Thales Alenia Space UK Ltd, UK

### Monday 17<sup>th</sup> October

- 09:00 16:30 Registration Open

- 14:00 16:00 Introduction & Key Note Speaker (120 min)

- 16:30 17:30 Networks & Protocols Short (60 min)

### Tuesday 18<sup>th</sup> October

- 09:00 11:30 Registration Open

- 09:00 11:00 Networks & Protocols 1 Long (120 min)

- 11:30 13:00 Test & Verification Long (90 min)

- 14:00 15:00 Onboard Equipment Long (60 min)

- 15:00 16:00 Poster Session (60 min)

- 16:00 18:00 Components Long (120 min)

### Wednesday 19th October

- 09:00 11:30 Registration Open

- 09:00 11:00 Components Short (120 min)

- 11:30 12:50 Test & Verification Short (80 min)

- 13:50 14:50 Networks & Protocols 2 Long (60 min)

- 15:20 16:40 Missions & Applications Short (80 min)

Programme is subject to change

# Monday 17<sup>th</sup> October

## **Networks & Protocols (Short)**

### A Novel Encoder for DC-Balanced SpaceWire

Christopher M. Rose Johns Hopkins University Applied Physics Laboratory Laurel, Maryland, USA Christopher.Rose@jhuapl.edu Steve S. Cho Johns Hopkins University Applied Physics Laboratory Laurel, Maryland, USA Steve.Cho@jhuapl.edu

Jarrett T. Wehle Johns Hopkins University Applied Physics Laboratory Laurel, Maryland, USA Jarrett.Wehle@jhuapl.edu

Abstract— A DC-balanced encoding for SpaceWire traffic offers several advantages in flight hardware design. Conventionally, block encoding techniques have been used. In this paper, a novel cycle-stretching method is described which takes advantage of SpaceWire's feature of embedding clock in data. This feature allows variable-length periods to be used opportunistically to perform DC-balancing of a SpaceWire stream, without using block encoders or relying on excursions from SpaceWire protocol. Such period-adjusting encoders can show high efficiencies for randomly generated SpaceWire traffic, particularly when paired with lookahead methods.

An encoder whose output can be decoded by conventional SpaceWire receivers is presented. Such an encoder produces a data stream which, while being DC-balanced, can be analyzed by conventional test equipment (e.g. link analyzers) without additional hardware.

The efficiencies of multiple encoders are characterized. Several worst cases are considered. An encoder is tested with flightlike data from integration testing of DART (Double Asteroid Redirection Test) a NASA spacecraft which uses a SpaceWire network.

Keywords—SpaceWire, Encoder, Cycle-Stretching, DC-Balanced, AC-Coupled.

#### I. INTRODUCTION

Institutions that use SpaceWire possess a significant amount of SpaceWire-specific test, integration, and debug infrastructure. Not only hardware, such as link analyzers, data recorders, protocol checkers, but also supporting software, test procedures, and, significantly, the accumulated institutional knowledge.

The advantages of AC-coupled SpaceWire are well understood.[1,2] Prior papers have proposed encoding techniques for DC-balancing SpaceWire as an enabler for ACcoupling. Several block encoders have been offered.[3,4] Other approaches have included PRS modulation—combining SpaceWire signals with a pseudorandom sequence—and

XXX-X-XXXX-XXXX-X/XX/\$XX.00 ©20XX IEEE

Matthew M. Gile Johns Hopkins University Applied Physics Laboratory Laurel, Maryland, USA Matthel.Gile@jhuapl.edu Kirk N. Volland Johns Hopkins University Applied Physics Laboratory Laurel, Maryland, USA Kirk.Volland@jhuapl.edu

eliminating the strobe lines entirely.[5] All these proposed methods, with encoders that either break from the SpaceWire protocol,[6] or that otherwise obscure the packets' contents, undermine the value of existing infrastructure.

This is the problem our method was developed to address: to provide an encoder that is DC-balanced, without diverging from the SpaceWire protocol or rendering the traffic 'on the line' illegible. We hope to do so while maintaining an efficiency high enough to make the encoder competitive with conventional block encoding methods.

#### II. DC BALANCING AND CYCLE STETCHING

For an AC-coupled SpaceWire to work, the transmit streams on both sides of a link must each be DC-balanced; that is, for each signal, the number of 1's and 0's must be equal, considered over a 'long enough' interval. The cumulative difference between the number of 1's and 0's is called the 'cumulative disparity', or simply 'disparity'. We compute separate disparities for the data and for the strobe. These must always remain less than some figure we will call 'maximum disparity', whose value is dependent on features of underlying hardware.

The basic encoding of SpaceWire demands that either the data line or the strobe line must toggle between adjacent clock periods, but not both. In this way, the clock is encoded in the transmitted signals, and can be recovered by the receiving node without any explicit clock signal crossing the link. This reduces hardware and eliminates concerns about clock/data skew.

But this also offers an overlooked opportunity. A SpaceWire transmitter could delay transitions in both data and strobe lines simultaneously; in such event, no new data is transmitted.

What if a node could be made to selectively delay transitions for the purpose of reducing the cumulative disparity on data and strobe signals? Such a node would pay a penalty in throughput, as the time of these additional transmit cycles will then be included, in which no new data is being transmitted.

Supported in part by a Janney Grant from Johns Hopkins University Applied Physics Lab, 2022.

A stream could be constructed to have a zero average disparity on both lines, data and strobe, and thus be ideal for ACcoupling. Also, such a SpaceWire signal would be interpreted at the receiver at as normal SpaceWire, adhering fully to the protocol, and with no additional decoding required. Further, the SpaceWire signals moving across the link would be readily interpretable by existing test and debug tools.

We have named this encoding method 'cycle-stretching.' A minimal implementation of such a method requires few logic gates beyond what is necessary for an unencoded SpaceWire node.

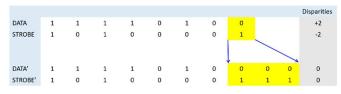

As an example, Figure 1 presents the bit pattern for a NULL token, the most common token on a SpaceWire link. On the upper rows, the data and strobe signals of the NULL are shown; in the right-hand column, we see that both the data and strobe signals have nonzero disparities. That is, there are two more 0's than 1's (assuming the parity for the prior character is zero) in the data bits, producing a +2 data disparity. There are two more 1's than 0's in the strobe bits, producing a net -2 strobe disparity.

Cycle-Stretching a SpaceWire NULL

Figure 1: Cycle-Stretching a SpaceWire NULL

At the level of a single NULL, these disparities may be tolerable by the hardware for an AC-coupled link. However, if a run of consecutive NULLs is sent, the cumulative disparities will grow linearly until the AC-coupled link fails.

The lower rows of Figure 1 show our cycle-stretch encoding. One cycle of data and strobe, conveniently, has values that can counterbalance the disparities in the character. The last cycle of the NULL, highlighted in yellow, has been stretched across three consecutive periods, producing a NULL that has zero disparities. The data conveyed on the data and strobe lines, however, is not changed; the receiving node just sees a NULL. It takes 25% longer to be transmitted.

It is a little suspicious how this feature has remained latent in the protocol this whole time. It is as if the inventors of SpaceWire anticipated our need, and embedded this ingenious degree of freedom in the protocol itself, just for us to find it.

#### III. THE SPLIT DIFFERENCE METHOD

Not all examples work out so conveniently as our NULL above. Often the magnitude of the data and strobe disparities will be different. In these cases, we can zero both disparities within the same character, by stretching two different data/strobe pairs a differing number of cycles.

We call this the split difference method. If there are two different disparities,  $D_m$  and  $D_n$ , where  $D_m$  is the disparity with the larger absolute magnitude, then we would perform stretches with different numbers of cycles:

Major stretch =

$$D_n + \frac{1}{2}(D_m - D_n)$$

(1)

Minor stretch =

$$\frac{1}{2}(D_m - D_n)$$

(2)

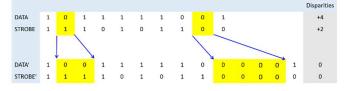

Figure 2 shows an example that will make this clear. Cycle-Stretching with Split Difference

Figure 2: An Example of the Split Difference Method

In this case,  $D_m = 4$ , and  $D_n = 2$ . As the expressions above indicate, the major stretch should be three cycles (or periods) long, and the minor stretch should be one.

There are additional details to consider to implement a full DC-balanced encoder using cycle-stretching, even in this simplest mode—with each character being individually balanced. Not all four combinations of data and strobe (0/1, 0/1, 1/1, and 1/0) may occur in some characters; in these cases, the disparity of the unstretched character should be added to that of the subsequent character. Timecodes must be free of any cycle stretching, as it is a requirement to transmit them with minimum delay. An upper limit to the number of consecutive stretch cycles must also be chosen and enforced.

#### IV. WORST CASES AND EFFICIENCIES

The largest cost for per character DC-balancing via cycle stretching is the reduction in net transmission rate, and accompanying reduced ability to predict the real data rate, of a cycle-stretched link.

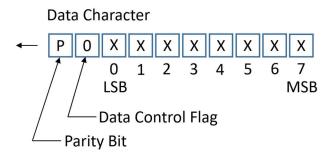

SpaceWire data characters, which are by far the most common in SpaceWire traffic, are inherently unbalanced.

Figure 3: Structure of a SpaceWire Data Characters

For a data character, the data-control flag must be zero. Also, the parity bit is given as even; but, for a ten-bit character, it is not possible to compose a character with an equal number of 1's and 0's that also has an even parity (i.e. ten bits, balanced as five 1's and five 0's, can only have odd parity.) Therefore some amount of cycle-stretching will always be necessary. For a conventional block encoder, the resulting data rate reduction is easily quantifiable regardless of the input stream. A block encoder can provide a consistent data rate because the worst-case is enforced everywhere; that is, the same number of bits are added to each token. For instance, for an 8b/10b encoder, every eight bit input character produces ten bits of encoded data. In contrast, a cycle-stretch encoder can produce a range of efficiencies, dependent on statistical qualities of the data to be encoded.

For cycle-stretch encoders, the fraction of bandwidth consumed by cycle-stretching is variable, and dependent on the contents of the input stream. The method takes advantage of input streams that are well-balanced, but must use more transmit cycles to encode input streams that have large disparities.

The simplest application of cycle-stretching for DCbalancing would perform cycle-stretching in each character to arrive at zero or near-zero disparities. Such an encoder was implemented by the authors by modifying SpaceWire node IP written at GSFC (Goddard Space Flight Center) by Glenn Rakow et .al. The node was incorporated into a ten-port router similar to those used in the avionics for Parker Solar Probe and IMAP (Interstellar Mapping and Acceleration Probe), both NASA missions built by Johns Hopkins University Applied Physics Laboratory in Laurel, Maryland. The design was implemented on a Microchip ProASIC 3000.

For long runs of worst-case data, this simple cycle-stretch encoder could approach a Manchester encoder in its efficiency. Consistent worst-case or near-worst-case input data would nearly double the bandwidth required to transmit each packet, if the minimal interval between transitions were kept unchanged.

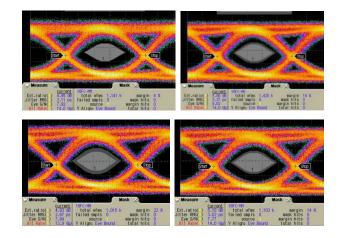

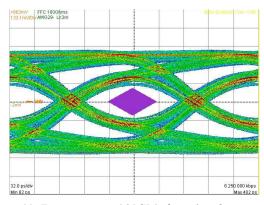

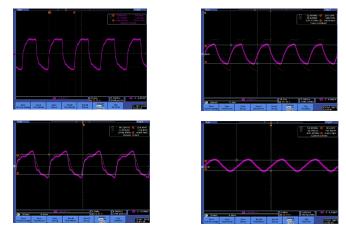

Figure 4 below shows an oscilloscope image of the traffic on the router, with the router's cycle-stretch encoders enabled. It doesn't require a very sophisticated eye to see that, for the simple implementation, the added 'stretch' cycles significantly reduce the efficiency of the encoders. However, and notably, the downstream receivers for these packets, connected avionics hardware or GSE test equipment, interpreted them with no errors, without any additional decode logic required.

Figure 4: Traffic on a Simple Cycle-Stretching Router Implementation

We measure the efficiency of an encoding method by calculating the number cycles of input data to be encoded divided by the resulting number of encoded cycles. For a stream of generated packets of random length, with each data bit randomly selected with 0's and 1's being equally likely, the resulting efficiency of this simple cycle-stretch encoder is approximately 0.66. This simplest application of cyclestretching would be appropriate only where there was significant available bandwidth overhead. One can easily compose worst cases for cycle-stretch encoding, with either the transmit data or strobe signal containing an arbitrarily long series of either ones or zeroes. While these worst cases are bad outcomes for the encoder efficiency, they are unlikely to occur in practice. A packet of all zeros is uninteresting because it conveys little information. In such a worst-case situation, an encoder could insert NULL characters interior to packets, or between packets, to create opportunities to perform cycle-stretching and reduce disparities.

Another worst-case exists: a case where the input data to be encoded is composed entirely of timecodes. Nothing in the SpaceWire protocol prevents this scenario. Obviously, an input stream that is nothing but back-to-back timecodes would foil any cycle-stretching method that left timecodes unaltered. In practice, such a usage could be proscribed a priori.

A SpaceWire node could be modified to improve its efficiency while using cycle-stretch encoding. It could compress the data to be transmitted, or cherry-pick only interesting data to be sent. It could combine incoming data with some easily derived sequence, for instance one produced by an LFSR, (as suggested by Kisin and Rakow, [4]) to improve the amount of activity. All these actions, however, make interpretation of packet traffic, for instance through a link analyzer, more difficult. Making packets less legible 'on the line' is counter to the aims of this project.

#### V. LOOKAHEAD METHODS

Most flight-like SpaceWire data steams possess, to varying degrees, the tendency of reversion to the mean. The data to be sent, over a sufficient time period, averages to roughly half 1's and half 0's. This feature can be exploited.

A more efficient cycle-stretch algorithm, with the ability to see a fixed number of upstream characters (e.g. characters to be sent in the future), and a tolerance for disparities below a specified threshold, could choose to defer some balancing tasks. It could wait, opportunistically, allowing some positive and negative disparities to cancel one another, reducing the total number of stretch-cycles necessary. Such an encoder would, ideally, employ cycle-stretching only to correct disparities as they approached the threshold, that is, the maximum tolerable disparity.

We have investigated using such look-ahead methods to reduce the amount of cycle-stretching required.

Two parameters are used. One is the number of periods ahead the algorithm can see in its decision-making, called 'lookahead distance'; the second is the maximum disparity to be allowed.

The authors wrote a C language model to demonstrate the impact on encoder efficiency of these features: lookahead method, lookahead distance, maximum allowable disparity. The C code model is a (somewhat) rapid tool for estimating an algorithm's efficiency for a given data stream. Additionally it can produce randomized input data as well as that of some cases of specific interest. The authors hope to be able to provide this model to interested readers.

In our first method, what we have called 'naive lookahead,' the difference in the accumulated disparities between the lookahead character and the current character to be transmitted is divided by the lookahead distance (which is the number of periods separating them in the transmit character sequence.) The rounded result is then the current disparity to be zeroed via cycle-stretching in the current character. This calculation is repeated twice, to find the current disparity for the data and for the strobe. The decimal fractions of disparities that are rounded down are not discarded, but added to the differences for the next cycle's calculations.

Some things to note about naive lookahead: it is likely to be inefficient for input data that undergoes sudden statistical changes. Also, because it uses division, it is subject to errors in accuracy when implemented in any finite digital hardware. It requires some exception cases for the beginning and end of any finite run of input data.

A second method we attempted uses a 'rolling average' in a similar fashion. For each new character to be transmitted, we would add the lookahead character's disparity, and subtract the current outgoing character's disparity, to a rolling average. This rolling average then would be divided by the lookahead length, to derive the current disparity to be balanced. This same calculation would be employed for data and for strobe, to produce two disparities.

Both of these lookahead methods would require significantly more logic and memory to implement. In both of these methods, the accumulated disparities for both the lookahead character and the current (outgoing) character would need to be calculated. Obviously, encoder latency will be increased in naive lookahead and in rolling averaging methods.

Initial results were not encouraging. The efficiencies were higher than for the simple cycle-stretching method, but the resulting disparities increased over time.

Both of the lookahead methods are inherently 'leaky' in that they use averaging and division. To ensure that DC-balancing is maintained, a 'clean-up' stage was added to process the output of the lookahead stage. This clean-up stage would perform simple single-character disparity zeroization only for characters whose disparities exceeded a maximum allowable disparity.

Subsequent to the addition of this second stage, the efficiencies were higher and the disparities were well-behaved.

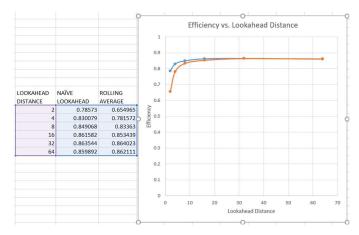

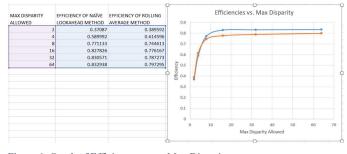

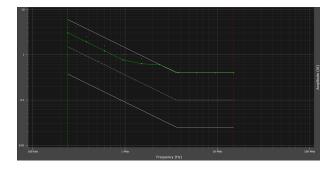

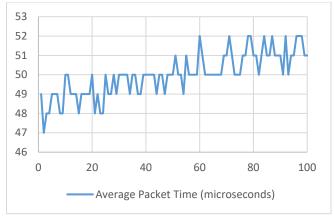

In one series of simulations, the encoding of the same long sequence of randomly-generated data was performed iteratively with a larger lookahead value each time. Figure 5, below, captures the results, showing that a larger lookahead distance, for the same given disparity thresholds, results in higher efficiency.

Figure 5: Graph of Efficiency versus Lookahead Distance

In a second test, the same fixed lookahead value was used, while the simulation was iterated with ascending values of the disparity thresholds—the encoder will ignore higher fluctuations in the instantaneous disparities so long as they remain below the thresholds. Figure 6 shows, not surprisingly, the higher thresholds resulted in reduced amounts of cyclestretching performed, and thus higher efficiencies.

Figure 6: Graph of Efficiency versus Max Disparity

For sufficiently random data, it's clear that the naïve lookahead method is sufficient for a high efficiency, with a reasonable lookahead distance and disparity threshhold. For less random data, the rolling averages method proved more consistently successful.

Additionally, lookahead simulations were performed using data recorded from integration tests of the DART spacecraft. DART, the Double Asteroid Redirection Test, is a recent NASA mission undertaken by JHUAPL to demonstrate planetary defense. Several runs of different samples of data produced a range of efficiencies, from dismaying (0.721749, for data with a lot of zeroes) to gratifying (0.822454). These results were produced with a rolling average, a lookahead distance of 16, and a max allowed disparity of 32.

As a final note: in any flightlike SpaceWire traffic, there are quiescent periods with no packets being transmitted. Such intervals of idleness can by used to reduce or eliminate disparities, by performing cycle-stretching over the series of NULL characters that must be sent during the gaps in traffic. The above efficiency discussions assume that all packets are back-to-back, without any quiescent periods.

#### VI. FUTURE WORK AND APPLICATIONS

More work remains in developing an understanding of how to find the maximum allowable disparity is for a given piece of SpaceWire hardware. The ability to measure that value accurately is crucial to the performance of any cycle-stretching encoder.

Also, existing algorithms modeled in C need to be converted to syntheziable HDL so that the resources required to implement them can be quantified.

It's clear, also, that there are better cycle-stretch algorithms waiting to be discovered. For any given sequence of characters, there must exist one or several optimum cycle-stretch sequences that will produce a minimal-length DC-balanced sequence, and we currently have no idea how to find them.

AC-coupled SpaceWire offers a higher degree of robustness particularly when charging spacecraft internal and external components occurs, for instance due to immersion in plasmas. This is of particular concern in deep space missions. For this reason, AC-coupled SpaceWire, using a cycle-stretch encoding, has been baselined for the proposed Interstellar Probe mission.[7] It is our goal to have a viable, robust, and efficient encoder ready when called on for that mission.

#### REFERENCES

- M. Suess, J. Ilstad, W. Gasti, "Galvanic Isolated SpaceWire Links, Requirements, Design Options and Limitations," 2009, ESA Workshop on Reliable Power & Signal Interfaces

- [2] [2] M. Epperly and S. Torno, "Galvanically Isolated SpaceWire," International SpaceWire Conference 2014

- [3] [3] Cliff Kimmery, "DC-Balanced Character Encoding for SpaceWire," International SpaceWire Conference 2011

- [4] [4] M. Epperly and S. Torno, Ibid.

- [5] [5] A. Kisin and Glenn Rakow, "New Approaches for Direct Current (DC) Balanced SpaceWire," 7th International SpaceWire Conference, 2016.

- [6] [6] "SpaceWire Links, Nodes, and Networks", ECSS Standard ECSS-E-ST-50-12C

- [7] [7] Kinnison et. al. "Conciderations for a Pragmatic Interstellar Probe Mission,", December 2020, American Geophysical Union, Fall Meeting 2020.

## Evolutions of SpaceWire Protocols for Deterministic Data Delivery

Networks and Protocols, Short Paper

Krzysztof Romanowski\*, Piotr Tyczka ITTI Sp. z o.o. Poznań, Poland {Krzysztof.Romanowski,Piotr.Tyczka}@itti.com.pl

Abstract—The primary application domain of SpaceWire networks has traditionally been payload data handling, whereas communication related to command and control has been implemented with other types of networks, since the basic SpaceWire protocol cannot provide deterministic data delivery. There have been several protocols proposed that add SpaceWire, including SpaceWire-RT, determinism to SpaceWire-T, and SpaceWire-D. This paper presents further evolutions in this area based on SpaceWire-D as the starting point. A new protocol called Mixed Criticality Message Passing protocol (MCMP) is proposed, together with a new intermediate protocol for transferring data in time slots instead of RMAP, called the MCMP Register Access Protocol. The protocol has been implemented and tested in the MOST-X network simulator.

Keywords—network protocols, SpaceWire, deterministic data delivery, mixed criticality systems, simulation

#### I. INTRODUCTION

Adopting a single common network for all on-board communication can lead to reduction of complexity, mass, and power demand. However, the timeliness requirements of command and control applications call for deterministic data delivery with guarantees on latency and jitter that are absent in the basic SpaceWire protocol [1].

Several protocols have been proposed that add determinism to SpaceWire, including SpaceWire-RT [2], SpaceWire-T [3], and notably SpaceWire-D [4]. The latter schedules SpaceWire traffic, defining four virtual buses of varying classes of determinism and multiplexing the traffic on them in the time domain, with time slots defined by SpaceWire time-codes sent by a network manager. The Remote Memory Access Protocol [5] is used as the transport mechanism between network nodes.

This paper describes evolutions in this area that were proposed in the ESA-funded project *SpaceDet*. Taking SpaceWire-D as the starting point, a new protocol called Mixed Criticality Message Passing protocol (MCMP), is introduced, together with a new intermediate protocol for transferring data in time slots instead of RMAP, called the MCMP Register Access Protocol (MRAP).

Section II presents background information, including basic features of SpaceWire-D and some limitations. The core components of the proposed MCMP protocol are the subject of Sections III, IV, and V. Testing and validation are discussed in Section VI, and Section VII presents conclusions.

David Jameux ESTEC European Space Agency Noordwijk, The Netherlands David.Jameux@esa.int

#### II. BACKGROUND

The SpaceWire-D protocol schedules SpaceWire traffic, defining four virtual buses of varying classes of determinism and multiplexing the traffic on them in the time domain, with time slots defined by SpaceWire time codes sent by a network manager. While the protocol seems very well suited for traffic comprising RMAP transactions of not very long packets in networks of moderate complexity, there are some characteristics of SpaceWire-D for which it is worthwhile to analyse their suitability for less typical use cases and to investigate possible alternative solutions.

The mechanism used in SpaceWire-D for defining the time-slots is the SpaceWire time-codes, which can – according to the SpaceWire-D specification – be used either:

• directly: each time code received by a SpaceWire-D initiator defines the beginning of a time-slot ([4], Clause 5.5.2.1); or

• indirectly: time-slots are defined by a local timer in the SpaceWire-D initiator, with time codes used for synchronizing the slots; a time code that arrives too early or too late (i.e. beyond specific limits) with respect to the timeslot boundary based on the local timer causes the timer to update its time and correct the time-slot boundary immediately ([4], Clause 5.5.2.3).

Although the latter tolerates occasionally missing time codes, in both methods the time codes are expected to be generated at each time-slot boundary. The frequency of the codes is thus related to the needs of the synchronous control applications that require the deterministic protocol. These are typically used in control loops of frequencies of 1 Hz to 1 kHz. For such a range of frequencies, and in addition for possibly less frequent large scientific data transfers, all running on the same network, the mere 64 time-slots might be not flexible enough.

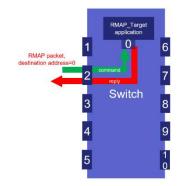

All the traffic under SpaceWire-D is carried as RMAP transactions. This has the advantage of RMAP being already implemented in a number of devices, which – when acting as SpaceWire-D (and RMAP) target nodes – basically do not require any additional protocol support, the whole burden of SpaceWire-D implementation involving only the initiator nodes. Using RMAP is naturally convenient when the traffic intended to be sent via SpaceWire-D is composed of transactions (of a command-reply type), and of RMAP transactions in particular.

However, such use might potentially conflict with regular RMAP applications as far as memory addressing space is

This work has been funded by the European Space Agency under contract no. 4000125047/18/NL/BJ/zk.

<sup>\*</sup>Corresponding author

concerned. Also, the details of using RMAP in SpaceWire-D are not necessarily compatible with regular RMAP usage, the most evident example being probably the extra word added to the RMAP payload on the SpaceWire-D Packet Bus due to possible segmentation. On the other hand, the overhead of all the data in RMAP headers may be more than is needed for the deterministic transmission, and even the transactional character with the acknowledgements may not always be required.

Finally, fault detection, isolation, and recovery (FDIR) is a valid aspect for any communications protocol, and particularly in applications where deterministic transmission is expected. The SpaceWire-D draft standard addresses fault detection (and prevention; [4], Clause 5.16), but not isolation or recovery. This is a potential area for improvement.

As a possible means for the improvement, modifications and additions to SpaceWire-D are proposed that can be classified as three areas: time coordination, intermediate protocol, and FDIR mechanisms. The name for the resulting modified protocol is MCMP. Time coordination

MCMP uses local timers for time-slot definition and a means of synchronising the SpW Nodes local timers – e.g. the SpaceWire Time Distribution and Synchronization Protocol (SpW-TDSP) [6].

Due to the flexibility of structuring the epoch, it is possible to define long epochs and short time-slots, for use cases involving both slow and fast periodic transfers. IN cases where long time-slots are useful (for transmission of large data packets), the SpaceWire-D mechanism of multislots can be used. There is also a possibility of using nonuniform time-slot sizes, with the effect basically similar to that of using multi-slots, but with the definition of nonuniform sizes being permanent for a given system and common for all masters<sup>1</sup> rather than being created ad hoc by a specific master opening a multi-slot virtual bus. Short timeslots can be appropriate for time-critical traffic on static and dynamic buses, while long slots can be useful for high volume data on asynchronous and packet buses.

The following principles apply to MCMP:

1. Local timers are mandatory at master nodes and optional at slave nodes. Slave nodes respond to master nodes and do not themselves initiate transactions, thus they do not need to be aware of time, time-slots, and schedules. It is the responsibility of master nodes to maintain the time-slot sequence and obey the schedules. However, slaves are required to close master-initiated transactions within a bounded time known to the master(s).

2. The time-slot sequence needs to be the same at all master nodes. Since time codes are no longer used to define the time-slots, the slots have to be identified by relation to local timer values of their beginnings, relative to the beginning of the epoch. The beginning and length of the epoch need to be consistent among the master nodes and should be set at system initialization time.

3. The schedule tables are maintained by each master node and manipulated by opening and closing virtual buses. The tables may be the same at each master node (simple scheduling) or they may be different (concurrent scheduling), provided there is no conflict in the nodes' usage of network resources (ports/links). Assuring there is no such conflict is the responsibility of applications manipulating the tables and is a functionality outside the scope of MCMP.

Synchronization of the local timers of nodes is the responsibility of SpW-TDSP (or of any other time synchronisation means) and is beyond the scope of MCMP. However, due to the way MCMP works, there are some requirements and notes:

a. A master node is not allowed to initiate any transaction until its local timer has been synchronized, including any latency, jitter, and drift mitigation that may be applied – unless the node is also the SpW-TDSP initiator (or unless there is only one SpW-MCMP master).

b. The messages of any SpW-TDSP can only be channelled through a specific virtual bus of MCMP. It may be adopted that at least the first MCMP static bus, allocated to the first time-slot in an epoch, is dedicated to SpW-TDSP transactions; and that the SpW-TDSP initiator runs in an MCMP master node and needs to always have information on the epoch origin and length, and at least on its dedicated time-slot(s).

c. MCMP masters have also the role of MCMP slaves when receiving time data from the SpW-TDSP initiator.

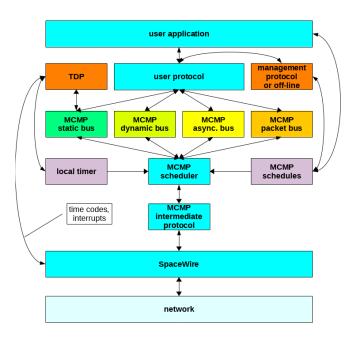

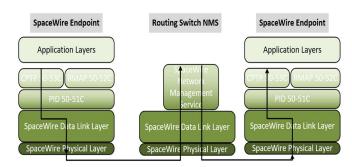

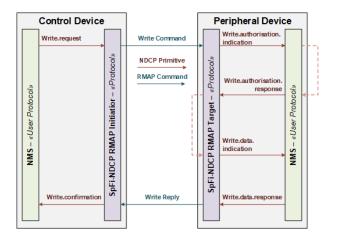

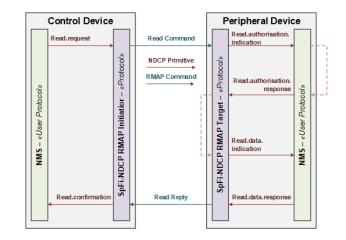

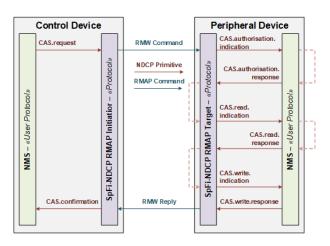

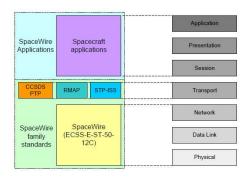

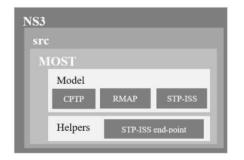

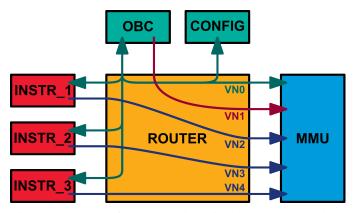

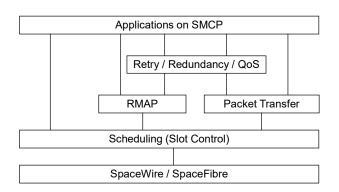

Fig. 1 shows the different elements of the MCMP functionality in a stack of protocols layers.

Fig. 1. Stack of protocols engaged in MCMP operation

#### III. INTERMEDIATE PROTOCOL

It is proposed that solutions alternative to RMAP be allowed for the "intermediate" protocol between user data units and SpaceWire packets.

At the upper layer of this functionality, somewhat related to scheduling, is the transaction model. The following two models – mutually exclusive -- have been proposed for MCMP:

<sup>&</sup>lt;sup>1</sup> The notions of *master* and *slave* are used in MCMP in place of the roles of *initiator* and *target* in SpaceWire-D.

1. [Primary model] "Acknowledged" – as it is in SpaceWire-D, where a complete transaction, scheduled in a slot, has to include both the command and the reply (and so RMAP write commands should set the 'reply' bit in the command field in the RMAP header; for RMAP read commands this is clearly the only option). The acknowledgement can be generated also for other protocols, and there need not be a one-to-one relation between the command and the reply packets (cf. aggregated acknowledgements in SpaceWire-T). The advantage to this model is the possibility of detecting transfer faults (e.g. loss of the command or the reply packet) at the master node.

2. [Secondary optional model] "Unacknowledged" – where the operation scheduled in a slot includes only oneway communication. This can be e.g. an RMAP write command with the 'reply' bit unset or a write-like command of some other protocol. This model is currently not within the SpaceWire-D specification.

Going down in the protocol stack, the intermediate layer uses some means of passing user data to the SpaceWire layer. The following two mutually exclusive solutions encapsulating the user data have been proposed for MCMP:

a. [Primary solution] A dedicated (with its own protocol ID) protocol based on RMAP.

While keeping the original RMAP header structure, the semantics of some of the fields can be customized for the new protocol. If some limits are placed on the RMAP functionality and address range, certain fields or bytes in the RMAP header can be freed for other use. For example, enough space in the header could be found for a long time-slot.

Specifically, the memory address field, no longer (or not necessarily) related to the same memory addresses as in RMAP, can also have a different semantics (addressing some registers of a special set) and leave some bits free. If the extended address is not used (e.g. because 40-bit address space is not needed and it is enough to be able to address 2<sup>32</sup> memory units), then 8 bits are freed for other use.

Altogether, the above change can provide as much as 24 bits of space for information specific to MCMP. It is proposed that this specific information includes the time-slot identifier. The SpaceWire-D protocol makes use of 64 time-slots, which can be identified with a 6-bit-wide field. Adopting SpW-TDSP for MCMP gives a possibility for a much larger number of time-slots. It is assumed that there are cases where having more than 256 time-slots in an epoch may be useful, so that a single byte for the time-slot ID is not enough and a 2-byte field should rather be adopted. The two bytes can occupy the place of the 'extended address' field and one of the 'data length' bytes of the RMAP header format.

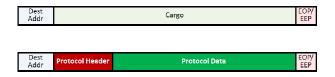

An example packet header format for the proposed MCMP is shown in Fig. 2.

Besides changes in the packet format, some of the RMAP command variants (e.g. the Read-Modify-Write) can prove unnecessary in MCMP, making a simplification of the protocol possible.

This RMAP-derived intermediate protocol for MCMP has been termed the MRAP (MCMP Register Access Protocol).

b. [Secondary alternative solution] Raw transmission: no encapsulation at all. In this variant, the user data unit is transmitted as is in an appropriate time-slot. The MCMP in this case can be seen as the SpaceWire-D protocol reduced to its upper layer of scheduling (Fig. 3).

#### IV. FDIR MECHANISMS

The current specification of SpaceWire-D provides means of detecting some faults: time-code errors (early, late, or missing), SpaceWire errors (link connect failures, reception of EEP), errors signalled in RMAP replies, and late or missing RMAP replies. These capabilities are extended in the proposed MCMP protocol with the following mechanisms.

1. Time-slot identification – already present in the current SpaceWire-D as "virtual bus ID" (concatenated with other parameters in the transaction ID field of the RMAP header). It is also present in the MRAP protocol. This ID makes it possible to match replies against commands, and to check whether the packet arrives in the proper time-slot.

2. SpaceWire interrupts. In a scenario where no multislots are employed, the interrupts are used for "hard limitation" of the time-slots, by forcing the routing switch to discard any packets that are being transferred at the time of a time-slot boundary.

3. Guard (silent) intervals defined to be in each timeslot or multi-slot. Allocated at the beginning and at the end of a time-slot, they can accommodate time-slot time skew and jitter.

#### V. TESTING AND VALIDATION OF MCMP

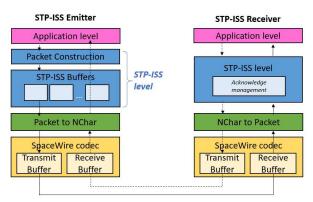

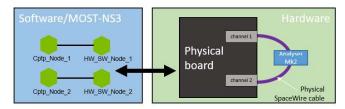

As a simulation environment the MOST-X simulator developed by Thales Alenia Space [7] based on ns-3 [8] was selected. The simulator was substantially extended so as to make it possible to be used for simulations of SpaceWire-D as well as its evolutions – the MCMP protocol.

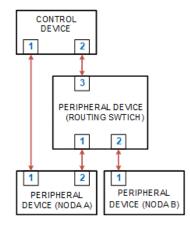

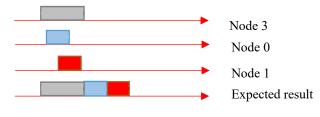

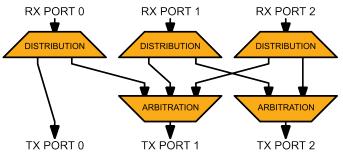

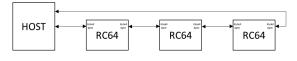

The network modelled in the simulator consisted of different variants of connections of RMAP nodes and switches; a representative example is shown in Fig. 4. The switch models were equipped with the ability to model a feature of the Cobham Gaisler GR718B switch of truncating packets on reception of time-codes or distributed interrupts, which could be used in support of SpaceWire-D protocol or its evolutions.

A number of data streams were defined, following the SAVOIR classes, and scheduled to use all types of buses: static, dynamic, asynchronous, and packet. Various time epochs were used, with time slot numbers ranging from 64 to 8000.

The tests showed that the simulator application is capable of simulating RMAP and SpaceWire-D in basic use cases, also with all the four SpaceWire-D bus types co-existing in the same simulation run. The latencies and throughputs recorded were as expected, given the assumed SpaceWire link data rate and the device latencies (which were taken to be similar to those reported in documentation of some SpaceWire devices available on the market, e.g. the SpW-10X routing switch.

| First byte transmitted    |                     |                     |                             |  |                           |  |

|---------------------------|---------------------|---------------------|-----------------------------|--|---------------------------|--|

|                           | Target SpW Address  |                     |                             |  | Target SpW Address        |  |

| Target Logical Address    | Protocol Identifier |                     | Instruction                 |  | Key                       |  |

| Reply Address             | Reply Address       |                     | Reply Address               |  | Reply Address             |  |

| Reply Address             | Reply Address       |                     | Reply Address               |  | Reply Address             |  |

| Reply Address             | Reply Address       |                     | Reply Address               |  | Reply Address             |  |

| Initiator Logical Address | BusT                | Transaction ID (LS) | Transaction Identifier (LS) |  | Time-slot Identifier (LS) |  |

| Address (MS)              | Address             |                     | Address                     |  | Address (LS)              |  |

| Data Length (MS)          | Data Length (LS)    |                     | Time-slot Identifier (MS)   |  | Header CRC                |  |

| Data                      | Data                |                     | Data                        |  | Data                      |  |

| Data                      |                     |                     |                             |  | Data                      |  |

| Data                      | Data CRC            |                     | EOP                         |  |                           |  |

Last byte transmitted

BusT=Bus type

Fig. 2. Fields of an MRAP write command

| First byte transmitted |      |  |                    |                        |

|------------------------|------|--|--------------------|------------------------|

| Target SpW Address     |      |  | Target SpW Address | Target Logical Address |

| Data                   | Data |  | Data               | Data                   |

| Data                   |      |  |                    | Data                   |

| Data                   | EOP  |  |                    |                        |

Last byte transmitted

Fig. 3. Unencapsulated packet of arbitrary SpaceWire protocol

#### VI. CONCLUSION

The general conclusion that can be drawn from the simulation results is that the new proposed MCMP protocol operates correctly and assures deterministic data delivery, which satisfies the fundamental prerequisite for it while simultaneously offers more flexibility in adapting to different network traffic types. Further work is needed to evaluate the protocol in a non-simulated environment and to compare this approach of placing most of the responsibility for deterministic transport on end nodes versus the alternative solution of placing that responsibility mostly on switches.

#### References

European Cooperation for Space Standardization, "SpaceWire – Links, nodes, routers and networks," ECSS-E-ST-50-12C Rev.1. Noordwijk: ECSS Secretariat, 2019.

- [2] S. Parkes, "SpaceNet SpaceWire-RT Initial Protocol Definition," Draft A Issue 2.1, University of Dundee, 2008.

- [3] S. Parkes and A. Ferrer Florit, "SpaceNet SpaceWire-T Initial Protocol Definition," Draft A Issue 3.1, University of Dundee, 2009.

- [4] S. Parkes, A. Ferrer, and D. Gibson, "SpaceWire-D Standard," Draft E, Issue 0.4, University of Dundee, 2015.

- [5] European Cooperation for Space Standardization, "SpaceWire Remote memory access protocol," ECSS-E-ST-50-52C. Noordwijk: ECSS Secretariat, 2010.

- [6] S. Habinc, A. Sakthivel, and M. Suess, "SpaceWire Time Distribution Protocol," Proc. 5th Int. SpaceWire Conf. Gothenburg 2013, pp.363-367.

- [7] B. Dellandrea and D. Jameux, "MOST: Modeling of SpaceWire Traffic," Proc. 5th Int. SpaceWire Conf. Gothenburg 2013, pp. 281-285.

- [8] https://www.nsnam.org

### SPACEMAN 2: Towards Multi-Protocol Network Management

Networks and Protocols, Short Paper

Jarosław Kwiatkowski, Krzysztof Romanowski\*, Piotr Tyczka ITTI Sp. z o.o. Poznań, Poland {Jaroslaw.Kwiatkowski,Krzysztof.Romanowski,Piotr.Tyczka} @itti.com.pl Rafał Renk Adam Mickiewicz University and ITTI Sp z o.o. Poznań, Poland Rafal.Renk@amu.edu.pl

David Jameux ESTEC European Space Agency Noordwijk, The Netherlands David.Jameux@esa.int

Abstract—Initiatives are on-going to upgrade the current communication technologies, for instance through the development of SpaceFibre or the adoption of Ethernet-based ground technologies. The complexity of the resulting networks and protocols calls for appropriate measures for management. This paper presents the development of an upgraded version of the SPACEMAN network management tool, originally supporting SpaceWire Networks composed of NDCP-aware devices and non-NDCP aware SpW-10X routing switches, which was then extended to handle SpaceFibre networks and more models of non-NDCP aware devices. Directions of its further development for Time-Sensitive Networking are also outlined.

#### Keywords—network management, NDCP, SpaceFibre, SpaceWire, RMAP

#### I. INTRODUCTION

In response to increasingly ambitious goals for future space missions and the associated needs of higher on-board data communication rates and quality, initiatives are ongoing to upgrade the current communication technologies and add new services, for instance through the development of SpaceFibre or the adoption of Ethernet-based ground technologies. The complexity of the resulting networks and protocols calls for appropriate measures for management.

For SpaceWire such a measure was introduced in the form of the Network Discovery and Configuration Protocol (SpW-NDCP) [1]. One of the first implementations of SpW-NDCP together with a network management application called SPACEMAN was delivered by ITTI in a project for ESA [2,3]. The SPACEMAN application originally supported SpaceWire networks composed of NDCP-aware devices and non-NDCP aware SpW-10X routing switches.

Evolution of the application continued so as to support the new protocols and new device models, as well as enable cooperation with other applications. The paper presents the results of that progress which found their place in the revised SPACEMAN 2 application or are being developed, within the frame of the ESA-funded project *Multi-Protocol On-Board Communications Network Manager* (*MultiSpaceman*). The major development direction is the support of more network protocols, beginning with SpaceFibre. In order to achieve this, the original SpW-NDCP had to be extended into a new version, described in a companion paper [4], with SpaceWire support retained though modified. Compatibility across versions is maintained: SPACEMAN 2 can handle both versions of NDCP. Pure SpaceWire or SpaceFibre as well as mixed SpaceWire/SpaceFibre Networks are supported. The next target network technology is IEEE 802.1-based Time Sensitive Networking (TSN).

The paper describes the key aspects of the advances made to SPACEMAN. Section II discusses the management protocols, their basic features, differences, and mechanisms they need to implement in order to support a network management application. Section III presents the device data model approach adopted in SPACEMAN to cope with the growing number of different incompatible devices. The devices supported currently by SPACEMAN are listed in Section IV. Other new features introduced to SPACEMAN are presented in Section V. Section VI outlines the directions for SPACEMAN development towards TSN. Finally, Section VII gives conclusions.

#### II. PROTOCOLS

Among fundamental tasks of a network management application are:

- (i) discovering network device presence and identity,

- (ii) discovering network topology,

- (iii) discovering network device state,

- (iv) discovering network device configuration,

- (v) setting network device configuration.

These tasks can be performed using active means (sending network packets and observing the results); some of them (except task (v)) in for some network technologies can also make use of passive means (listening to network traffic generated by the devices).

Key aspects of network device addressing are the presence or absence of a unique device address and receiver addresses in command packets and sender addresses in reply

This work has been funded by the European Space Agency under contract no. 4000132938/20/NL/AS.

<sup>\*</sup>Corresponding author

packets. The SpaceWire standard [5] does not define a notion of a permanent unique device. Instead, addressing depends on the placement of the sender and receiver devices in the network – the network path between them. A related characteristic is the absence of the sender address at the level of SpaceWire packets. As a consequence, a management protocol for SpaceWire needs to be given network topology information in order to be able to address its commands. It also cannot rely on passive listening to network traffic (apart from the fact that SpaceWire switches generally lack supporting facilities, like port mirroring). Moreover, due to the possibility of network loops, it needs some form of a unique device ID to recognize situations where the same device is accessed by different network paths.

The management protocol dedicated to SpaceWire: the SpW-NDCP, takes those circumstances into account. It also adds the notion of device ownership by a management application (or control device), which prevents overwriting device configurations by non-owners. A network manager application that employs the NDCP, performs the network discovery process, during which it learns the network topology and the paths needed for addressing, and assigns each network devices of the NDCP, and in particular of the following registers (NDCP fields) on each device:

- (a) a writeable one for the device ID,

- (b) a writeable one for device ownership information,

- (c) a readable one providing the number of the return port, i.e. the number of the port of the device through which the most recent command is received and the reply is sent back,

as well as an access control mechanism for protecting overwriting the device configuration by a non-owner.

Not many SpaceWire devices support the NDCP yet; examples of those that do include STAR-Dundee devices of the project that introduced the NDCP [6], Cobham Gaisler GR718B routing switches [7], and SpaceWire NDCP-aware nodes developed by ITTI in the *MultiSpaceman* project. An alternative protocol that could be used for network management is the RMAP [8].

It should be noted, however, that the RMAP, although standardised as to frame format and command-reply semantics, does not define the layout of the memory accessed. Different device models can have different register sizes, numbers, addresses, addressing modes (e.g. byte vs. word), byte order (most-significant vs. least-significant first), RMAP command types implemented (e.g. single address vs. incrementing address types), and, naturally, the values hold – their units, ranges, reset values, and meaning.

Access control similar to that available in the NDCP is not possible with the RMAP. As a result, network management should be constrained to a single control device (management application). Functions of the registers (a)-(c) discussed above need to be implemented as RMAP registers. The roles of registers (a) and (b) may be assigned to a single one, if there is only one that can be freely written by the application. Support of the functionality of register (c) is crucial for feasibility of network discovery via the RMAP. There are RMAP-aware devices without that functionality. When such a device is encountered, the problem of ambiguity of the return path appears, which can be solved by trying all possible return ports of the device; this approach is, however, inefficient and of limited scalability.

All those considerations are also applicable to SpaceFibre. The NDCP version 2, which has recently been proposed [4] and which is supported by the current version of SPACEMAN, is applicable to SpaceWire, SpaceFibre, and mixed SpaceWire/SpaceFibre networks.

#### III. DEVICE DATA MODELS

Originally the SPACEMAN network management application supported the SpW-NDCP and, as an exception, the RMAP as implemented in the SpW-10X switch. Since then, support for more device models has been added and the exception approach turned to a more systematic framework of device data models. The device data model specifies completely the method to access the device, including the protocol (SpW-NDCP, NDCP version 2, or RMAP) and, in the case of the RMAP, the availability and layout of the registers, the addressing mode, the destination logical address, and the RMAP key. The models to be used in a particular network discovery process form a prioritized list, which the user can set up by removing or adding models and changing their order (and thus priority).

There are four modes of selection of device data models by SPACEMAN:

- fully automatic: SPACEMAN tries each of the device data models on the list, until the device responds to an initial management command. The successful model is then adopted for further commands issued to the device. An auxiliary mechanism of a device signature can be used. The signature is the contents of specific bits of specific registers of the device that is considered a constant characteristic feature of the particular device model. This device data model is then used only if the appropriate device signature is found in the response to initial RMAP read commands (issued according to the currently tested model); otherwise the next model from the list is tried. If there is no reply from the device after trying all the models from the list, and the link to it is active, the device is marked 'generic': no information on it is available except its existence and place in the network.

- semi-automatic: This is similar to the fully automatic mode. However, if there is no reply from the device on an active link for any of the models on the list, the user can manually select a model to use for this device (supposedly a model that was not initially included in the list of models to be used).

- manual: For each device, before trying to send an RMAP query and get any reply, SPACEMAN asks the user to select a model to use for the query.

- manual in every cycle (relevant only in continuous discovery operation): This is similar to the semiautomatic mode. While in the (plain) manual mode SPACEMAN remembers the user's selection of the model for a specific device, in this mode such a selection needs to be made every time any device is encountered (even if a model for it was previously selected).

#### IV. DEVICE MODELS SUPPORTED

There are two aspects of device support by SPACEMAN. A device model can be supported as part of the managed network. Supporting this role of the device requires implementing communication between SPACEMAN and the device using any of the management protocols (NDCP or RMAP).

A device is also needed for SPACEMAN to physically connect its host computer to the managed network. This can be an internal SpaceWire board (e.g. PCI-based) or an external device with a SpaceWire interface and an interface connected directly to the host, like USB or Ethernet. Such a device is called the management gateway device; SPACEMAN communicates with it using an API or some dedicated protocol provided or documented by the device vendor. The range of supported management gateway device models was augmented, and they can now be monitored by SPACEMAN, with continuous display of the connectivity status of their network ports.

Table I lists the device models currently supported by SPACEMAN. For SpaceFibre devices, features specific for this technology, like virtual channels/networks and lanes are supported. In addition to real devices, there is also support under development for devices simulated in MOST-X.

| Device                                                                  | Discoveral<br>manageat<br>network p<br>devi                       | Capability of a<br>management<br>gateway device? |                            |

|-------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------|----------------------------|

| Device                                                                  | NDCP                                                              | RMAP                                             | Capabi<br>manag<br>gateway |

| STAR-Dundee SpW NDCP-<br>aware devices of the original<br>NDCP project  | yes                                                               | yes                                              | yes                        |

| STAR-Dundee SpW and SpFi<br>devices with STAR System API<br>3.10 or 4.0 | via a<br>USB-or<br>PCI/PCIe-<br>connected<br>PC-based<br>emulator | yes                                              | yes                        |

| STAR-Dundee SpW-USB Brick<br>Mk1                                        | no                                                                | yes                                              | no                         |

| STAR-Dundee SpFi and SpW<br>Router Breadboard                           | no                                                                | yes                                              | no                         |

| SpW-10X switch                                                          | no                                                                | yes                                              | no                         |

| TELETEL iSAFT SpW and SpFi PCIe boards                                  | no                                                                | no                                               | yes                        |

| Shimafuji GPWGB0012 switch                                              | no                                                                | yes                                              | yes                        |

| ITTI SpW node                                                           | yes                                                               | yes                                              | yes                        |

| ITTI SpFi node                                                          | yes                                                               | no                                               | no                         |

| Cobham Gaisler GR718B switch                                            | in<br>develop-<br>ment                                            | in<br>develop-<br>ment                           | no                         |

| Thales Alenia Space MOST-X simulator                                    | in<br>develop-<br>ment                                            | yes                                              | in<br>develop-<br>ment     |

#### V. OTHER NEW FEATURES

Other features developed recently include facilities for cooperation with other applications as well as various user interface additions and improvements. SPACEMAN now includes a TCP/IP server that can exchange device models (currently in the XML format) with external applications. The models can be sent both ways: SPACEMAN can send a model it has in its memory, whether just discovered from the connected physical network, created by the user in the built-in editor, or read-in from a file; SPACEMAN can also receive a model from an external application and do with it whatever could be done with a model read from file, e.g. use for comparison against another network (possibly the one being just discovered).

There are a number of user interface additions. While SPACEMAN sends packets to a network or receives them, it can be paused by a breakpoint, just before or just after sending or receiving. The user can then inspect the packet in the log and optionally edit its contents before resuming the paused transmission. Selected or all packets in the on-line packet log of SPACEMAN can be exported to a file.

Operations involving packet transmission, like network discovery, automatic configuration, or sending/receiving individual packets are equipped with time-related facilities. There are various options for the start time, end time, and repetition of an operation.

Finally, a SpaceWire/SpaceFibre network can be accessed and managed remotely, with the SPACEMAN application operating locally on the user's computer and a remote auxiliary connector application interfaced directly to the managed network while communicating with SPACEMAN over a TCP/IP link.

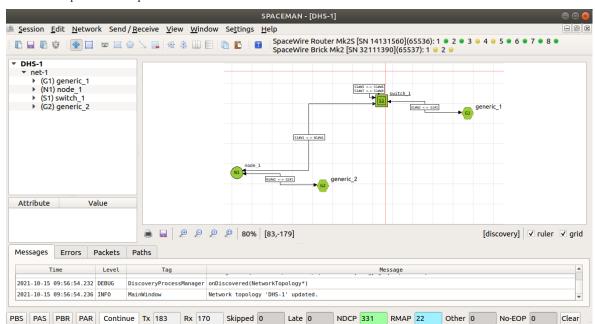

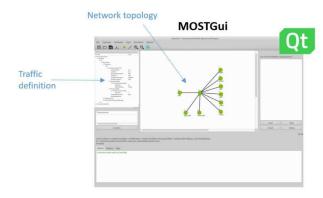

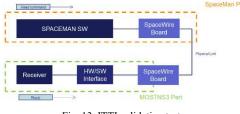

Fig. 1 displays a screenshot of SPACEMAN, showing the status bar of two management gateway devices, the tree and diagram of the discovered network, the log window, and the status bar with breakpoint controls and packet counters.

#### VI. BEYOND SPACEWIRE/SPACEFIBRE

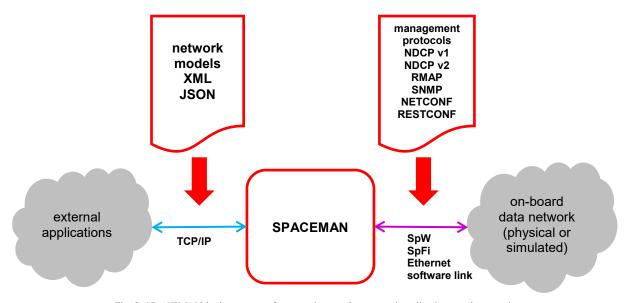

Following an increasing interest in application of TSN to on-board data networks, a follow-up activity is being prepared to extend SPACEMAN's applicability domain to TSN. This is a major development, since some properties of the Ethernet networks that are essential for network management are quite different than those described in Section II. The devices have a permanent unique MAC addresses, the data frames carry them as sender and receiver addresses (rather than paths), there may be a possibility of passive listening to traffic such as Link Layer Discovery Protocol. The management protocols are naturally quite Network Management Protocol, different: Simple NETCONF, or RESTCONF may be used for different devices to read and write configuration parameters. Moreover, because of the focus on time sensitivity and deterministic transmission, there are dedicated protocols for data stream definition and scheduling, like the IEEE 802.1Qcc [9], 802.1Qbv [10], and more of the 802.1 standard group. This will add network traffic design tasks to SPACEMAN with, performed either in the application or in cooperation with external applications. Fig. 2 shows SPACEMAN as part of the system with a network, external applications, connections, and protocols.

#### VII. CONCLUSION

Recent developments in the SPACEMAN network management application were presented, together with future work directions. It should be noted that network management is strongly dependent on the details of protocol support in the devices managed. For a network management tool, handling multiple protocols is inevitable, taking into account the variety of devices in use. It is worth noting, that tiny details in those devices, like the absence of the return port register in an RMAP implementation, can significantly affect the tool's operation and efficiency.

#### References

- European Cooperation for Space Standardization, Space Engineering – SpaceWire Network Discovery & Configuration Protocol, ECSS-E-ST-50-54 Draft 1.8. Noordwijk: ECSS Secretariat, 2016.

- [2] W. Hołubowicz, P. Lancmański, K. Romanowski, V. D. Kollias, and N. Pogkas, "SPACEMAN: A SpaceWire Network Management Tool," Proc. 6th Int. SpaceWire Conf. Athens 2014, pp. 99-102.

- [3] K. Romanowski, P. Tyczka, W. Hołubowicz, R. Renk, V. D. Kollias, N. Pogkas, and D. Jameux, "SpaceWire Network Management Using Network Discovery and Configuration Protocol," Proc. 7th Int. SpaceWire Conf. Yokohama 2016, pp. 45-50.

- [4] J. Kwiatkowski, K. Romanowski, P. Tyczka, and D. Jameux, "SpaceFibre and SpaceWire network management: NDCP version 2," submitted to 9<sup>th</sup> Int. SpaceWire and SpaceFibre Conf. Pisa 2022.

- [5] European Cooperation for Space Standardization, Space Engineering – SpaceWire – Links, nodes, routers and networks, ECSS-E-ST-50-12C Rev.1. Noordwijk: ECSS Secretariat, 2019.

- [6] S. Fowell, "Network discovery protocols final presentation", presentation at the TEC-ED and TEC-SW Final Presentation Days, Noordwijk, 2014.

- [7] GR718B Radiation-Tolerant 18x SpaceWire Router. 2020 Data Sheet and User's Manual, GR718B-DS-UM version 3.5, Cobham Gaisler, 2020.

- [8] European Cooperation for Space Standardization, Space Engineering – SpaceWire – Remote memory access protocol, ECSS-E-ST-50-52C. Noordwijk: ECSS Secretariat, 2010.

- [9] Institute of Electrical and Electronics Engineers, IEEE Standard for Local and Metropolitan Area Networks – Bridges and Bridged Networks – Amendment 31: Stream Reservation Protocol (SRP) Enhancements and Performance Improvements, IEEE Std 802.1Qcc-2018.

- [10] Institute of Electrical and Electronics Engineers, IEEE Standard for Local and Metropolitan Area Networks – Bridges and Bridged Networks, IEEE Std 802.1Q-2018.

Fig. 1. Example screenshot of the SPACEMAN application during work

Fig. 2. SPACEMAN in the context of managed networks, external applications, and protocols

# Tuesday 18<sup>th</sup> October

## Networks & Protocols 1 (Long)

### Deterministic SpaceWire / SpaceFibre ?

The Challenge !

Fotis Kostopoulos TELETEL SA Athens, Greece f.kostopoulos@teletel.eu

Barthelemy Attanasio *THALES ALENIA SPACE France* Cannes, France <u>barthelemy.attanasio@thalesaleniaspac</u> <u>e.com</u>

Felix Siegle European Space Agency (ESA) Noordwijk, Netherlands <u>felix.siegle@esa.int</u> Nikos Pogkas TELETEL SA Athens, Greece n.pogkas@teletel.eu

Hans-Joerg Beestermoeller AIRBUS Germany Bremen, Germany hans-joerg.beestermoeller@airbus.com Vangelis Kollias *TELETEL SA* Athens, Greece <u>v.kollias@teletel.eu</u>

Hans Corin BEYOND GRAVITY Gothenburg Sweden Hans.Corin@beyondgravity.com

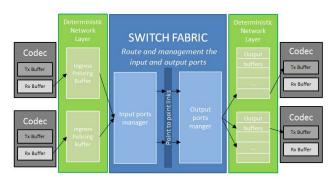

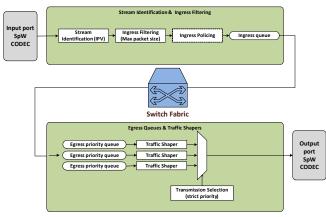

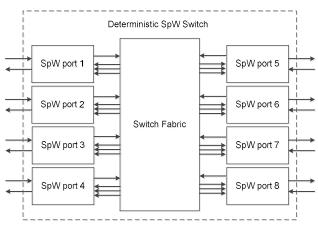

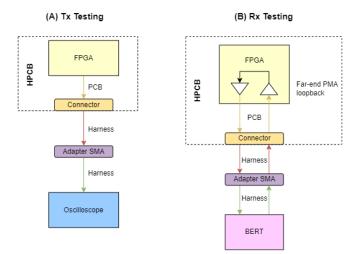

*Abstract*— This paper presents the results of an activity led by TELETEL in the area of onboard data networks aiming at defining a deterministic protocol layer for SpaceWire and SpaceFibre networks. The main objective of the activity is the development of a novel deterministic protocol layer for SpaceWire and SpaceFibre that works primarily at network level (i.e. within routing switch devices), allowing therefore to build fully deterministic networks with both protocol-aware and legacy SpaceWire/SpaceFibre nodes. The work is performed under the ESA study entitled "SpaceWire Network Management Service Suite definition and validation".

### Keywords—Spacewire, SpaceFibre, SpW, SpFi, TTE, TSN, AFDX, CBS, BAT

#### I. INTRODUCTION

The new concept elaborated by ESA for spacecraft avionics systems is bundled under the common Space Avionics Open Interface Architecture (SAVOIR). SAVOIR working group has issued a requirements document addressing the on-board communication system [1] where the term 'Deterministic / Determinism' is clearly defined. The objective of the activity presented in this paper is to introduce a novel deterministic protocol layer to the SpaceWire and SpaceFibre on-board networks according to the SAVOIR guidelines. However this results not only in functions ensuring the transmission within a certain time-window (SAVOIR definition), but also in the need for FDIR, network management, quality of service, etc., which are derived from system requirements (e.g. closed-loop control for AOCS). The applied control algorithms need to take into account the uncertain latencies that are a result of a non-deterministic network. For example, the time a sensor value was taken, until its computation inside the loop and the latencies to transmit the control command to the actuators. When drawing the chain of contributors, it is obvious, that the communication system is an essential element.

The MIL-STD-1553 protocol was and it is still used to provide determinism but for low data rate networks. Network topology has also evolved from the single master, as for MIL-1553 to multi master and switched networks. TTEthernet, SpaceWire and SpaceFibre are systems used in modern onboard architectures providing a much higher net data-rate. TTE is baselined for Ariane 6 and in use for the European Service Module for ORION. European contributions to the Lunar Gateway have baselined TTE such as IHAB in the respective systems as well. While combining high-speed communication, up to 1Gbit/s, with determinism, TTE appears to be very suitable. However, the effort for planning and configuring the network as well as for the verification process turned out to be high.

SpaceWire (and in the future SpaceFibre with much higher performance) is widely used in on-board architectures. SpaceFibre, in comparison with SpaceWire, is bringing already the possibility of a significantly higher datathroughput combined with means regarding the quality of service. However, determinism, as defined by [1], is not implemented yet in native SpaceWire. In order to extend the capabilities of SpW, some ideas have already been pursued resulting in the definition of N-MaSS for adding FDIR, a certain determinism with SpW-D or SpW-R targeting reliability. These concepts are adding an additional protocol layer (SpW-R, Spw-D) or additional monitoring functions (N-MaSS) to enable the functions.

#### II. INITIAL REQUIREMENTS FOR A DETERMINISTIC SPACEWIRE/SPACEFIBRE PROTOCOL

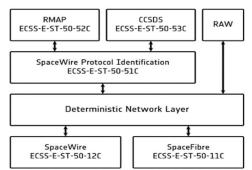

According to ESA [2], the main means of realizing determinism shall be to add an additional network layer as shown in the figure below.

Fig. 1. New protocol layer in the existing SpW/SpFi protocol stack

Any feasible design shall be capable of handling new deterministic and other legacy nodes, requiring thus an awareness of the protocol in the switches and the end nodes. The new protocol layer shall be developed in a way that it is mainly managed by the routing switches to keep compatibility with legacy nodes. New deterministic nodes may manage the new protocol layer directly while the new deterministic switches shall act as translator for legacy nodes. Traffic from and to legacy nodes shall be extended or stripped by the switch from the new deterministic layer. That way the switches act as translator between new and legacy protocols if necessary.

Deterministic and time accurate messaging requires all devices in the network to work with the same time basis. Since the native time synchronization mechanism on raw SpaceWire is not robust against failures such as delayed or erroneous time codes, a new concept shall be developed. The new time-code mechanism shall allow more robust and accurate time-code distribution in SpaceWire and SpaceFibre networks.

For deterministic network communication reliability is important. Therefore, the new deterministic layer shall also implement a concept for Fault Detection, Isolation and Recovery (FDIR). This shall include controllability of the new network layer from the user application as well as through the network. Optionally with a basic watchdog mechanism to control the status of the user applications through the network.

Before deriving a feasible approach for a network layer, a comparison with other approaches has been performed. For this activity and further to the past SpW initiatives (SpW-D, SpW-R, N-Mass) the approaches used in systems like AFDX, TTE and TSN have also been taken into account.

#### III. COMPARISON BETWEEN PROTOCOLS

From the analysis performed with the different approaches around determinism in the frame of other protocols than SpaceWire, it can be obviously concluded that depending on the need, the solution of mechanisms is not the same.

In fact, for example, AFDX does not bring a high level of determinism but at least controls the flow and ensures a bandwidth for every emitter. On the other hand, the 1553 defines every slot to communicate for every endpoint so it is fully deterministic by design but cannot bring any flexibility in flight due to its definition of traffic in a cyclic way.

Then, the two most interesting protocols which ensure a high level of determinism and flexibility in a network are the TSN and TTE which are both based on Ethernet. They are based on accurate synchronization of all the equipment within the network. The mechanisms implemented and defined in several norms ensure determinism. The interesting way to develop deterministic for SpaceWire is to take the advantages of these mechanisms without bringing the drawbacks such as the accurate synchronization, which adds several constraints to the implementation.

Comparing both protocols and mechanisms, after some research on previous studies and on research papers, it shall be noticed that there are many differences in terms of performance even if both are based on Ethernet. In fact, focusing on what is important in terms of performance but leaving the industrial problems apart, TTE seems to be a rather closed standard with only 3 priorities (TT, RC, BE) and without any flexibility.